TABLE II

MESFET NE710 DEVICE AND PACKAGE PARAMETERS

| MESFET NE710 Device Parameters:                    |             |

|----------------------------------------------------|-------------|

| 1 Forward Conduction Voltage (VF)                  | 0.50 V      |

| 2 Cutoff Voltage (VCUT)                            | 0.80 V      |

| 3 VSG for Max GDS (VGDSM)                          | 0.20 V      |

| 4 Built-in Potential (PHI)                         | 0.80 V      |

| 5 Device Max Current (CURON)                       | 56.0 mA     |

| 6 Device Current for VSG = 0 (CURDSS)              | 27.0 mA     |

| 7 Device Current for VSG = VGDSM (CURDSM)          | 13.5 mA     |

| 8 GM for VSG = 0 (GM0)                             | 75.00 mmho  |

| 9 GD Value for VSG = VDS = 0 (GD00)                | 80.00 mmho  |

| 10 GD Value for VSG = VGDSM (GDSM)                 | 4.00 mmho   |

| 11 CVSG Value for VSG = 0 (C0)                     | 0.230 pF    |

| 12 GVDS Value for VDS = VSG = 0 (CM0)              | 0.0000 pF   |

| 13 (-DVSG) Value for Large VDS (CMAX)              | 0.0000 pF   |

| 14 DVDS Value for Large VDS (CH)                   | 0.0300 pF   |

| 15 DVDS Value for VDS = 0 (CL)                     | 0.0253 pF   |

| 16 GVDS Value for Large VDS (CK)                   | 0.0000 pF   |

| MESFET NE710 Package/Circuit Parameters:           |             |

| 1 Source Inductance ( $L_s$ )                      | 5.00E-02 nH |

| 2 Gate Inductance ( $L_g$ )                        | 6.00E-02 nH |

| 3 Drain Inductance ( $L_d$ )                       | 0.00E+00 nH |

| 4 Parasitic Input Capacitance ( $C_{sin}$ )        | 0.00E+00 pF |

| 5 Parasitic Output Capacitance ( $C_{so}$ )        | 0.00E+00 pF |

| 6 Gate Pad Capacitance (CPAG)                      | 8.60E-02 pF |

| 7 Drain Pad Capacitance (CPAD)                     | 2.30E-02 pF |

| 8 Drain to Gate Pad Capacitance (CDG)              | 3.30E-02 pF |

| 9 Gate Metallization Resistance ( $R_g$ )          | 0.855 Ω     |

| 10 Substrate Leakage Resistance ( $R_{sub}$ )      | 1.00E+05 Ω  |

| 11 Source Metallization Resistance ( $R_{scont}$ ) | 1.900 Ω     |

| 12 Drain Metallization Resistance ( $R_{dcont}$ )  | 1.900 Ω     |

| 13 Source Bulk Resistance ( $R_{ss}$ )             | 0.000 Ω     |

| 14 Drain Bulk Resistance ( $R_{sd}$ )              | 0.000 Ω     |

| 15 Channel Time Delay ( $\tau$ )                   | 2.400 ps    |

mixer simulation yields more accurate conversion gain results than are possible with the original APFT algorithm. The advantages of the modified method over the original one increase as the input power is increased, i.e. as the nonlinearities become more pronounced. Those advantages are achieved without materially changing the length of the computation times.

## REFERENCES

- W. A. Curtice, "Nonlinear analysis of GaAs MESFET amplifiers, mixers and distributed amplifiers using the HB technique," *IEEE Trans. Microwave Theory Tech.*, Vol. MTT-35, pp. 441-447, Apr. 1987.

- J. H. Haywood and Y. L. Chow, "Intermodulation distortion analysis using a frequency domain harmonic balance technique," *IEEE Trans. Microwave Theory Tech.*, Vol. 36, pp. 1251-1257, Aug. 1988.

- S. Lezekiel, C. M. Snowden, and M. J. Howes, "HB model of laser diode," *Electron. Lett.*, vol. 25, no. 8, pp. 529-530, Apr. 1989.

- M. S. Nakhla and J. Vlach, "A piecewise HB technique for determination of periodic response of nonlinear systems," *IEEE Trans. Circuits Syst.*, vol. CAS-23, pp. 85-91, Feb. 1976.

- V. D. Hwang and T. Itoh, "Waveform balance method for nonlinear MESFET amplifier simulation," *IEEE MTT-S Int. Microwave Symp. Dig.*, 1989, pp. 581-584.

- R. Gilmore, "Nonlinear circuit design using the MHB algorithm," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-34, pp. 1294-1307, Dec. 1986.

- J. Dreifuss, A. Madjar, and A. Bar-Lev, "A full large signal analysis of active microwave mixers," presented at 16th European Microwave Conf., Sept. 1986.

- S. Kundert *et al.*, "Applying HB to almost periodic circuits," *IEEE Trans. Microwave Theory Tech.*, Vol. 36, pp. 366-378, Feb. 1988.

- A. Madjar, "An improved analytical AC large signal model for the GaAs MESFET," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1519-1522, Oct. 1989.

- Harris, "HMF-1200 Power GaAs FET," Product Data.

- Harris, Application Note 2: "Output Power Match for  $P_{1db}$  Power FET Chips," Feb. 1987.

- V. Rizzoli *et al.*, "General purpose HB analysis of nonlinear microwave circuits under multi tone excitation," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1650-1660, Dec. 1988.

- J. A. Higgins and R. L. Kuvas, "Analysis and improvement of inter modulation distortion in GaAs Power FETs," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-28, pp. 9-17, Jan. 1980.

- S. A. Maas, "Two tone intermodulation in diode mixers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-35, pp. 307-314, Mar. 1987.

- J. Dreifuss, A. Madjar, and A. Bar-Lev, "A novel method for the analysis of microwave two-port active mixers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 1241-1244, Nov. 1985.

## High-Frequency Efficient Reflection Multiplier

K. Rauschenbach, C. A. Lee, and M. V. Schneider

**Abstract** — We propose and calculate the performance of a new resistive balanced reflection multiplier capable of high-efficiency operation at submillimeter wavelengths, beyond the useful range of varactor-type multipliers. The multiplier and associated filters can be fabricated with monolithic thin-film techniques to sufficiently minimize high-frequency parasitic elements so that near ideal efficiencies can be realized. A closed-form distributed analysis is used to show that this reflection design can achieve a 6.7% third-harmonic conversion efficiency, an approximate 23% increase compared with an ideal resistive balanced transmission multiplier.

## I. INTRODUCTION

Resistive frequency multipliers are capable of higher frequencies of operation and wider bandwidths than state-of-the-art varactor diode multipliers [1], [2], which have an inherent frequency limitation caused by the saturation velocity of the neutral space-charge boundary. Resistive multipliers have several additional advantages which make them desirable for many applications requiring a local oscillator or a swept frequency source. They are very stable and easy to tune because their resistance provides enough loss to prevent parametric oscillation. Furthermore, a resistive balanced antiparallel diode configuration will inherently reject certain unwanted harmonics and will provide higher output power than single-diode multipliers [3]. Resistive frequency multipliers, however, are not widely used because they are significantly less efficient than varactor multipliers at lower frequencies [4]-[9]. The conversion efficiency for generating the  $n$ th harmonic of a resistive multiplier is fundamentally limited to  $1/n^2$  [10]-[13]. In contrast, a lossless nonlinear capacitance can theoretically convert up to 100% of the available generated power into any single harmonic [14], [15]. Unfortunately, the usable nonlinearity of the transition capacitance diminishes at frequencies above 100 GHz because the velocity of the boundary of the space-charge layer cannot

Manuscript received December 8, 1989; revised September 24, 1990. K. Rauschenbach is with the Lincoln Laboratory, Massachusetts Institute of Technology, Lexington, MA 02173.

C. A. Lee is with the Department of Electrical Engineering, Cornell University, Ithaca, NY.

M. V. Schneider is with AT&T Bell Laboratories, Crawford Hill Laboratories, Holmdel, NJ 07733.

IEEE Log Number 9041955.

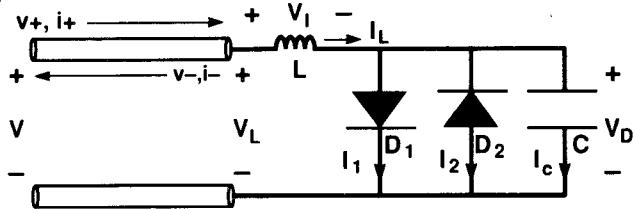

Fig. 1. Schematic diagram of a resistive balanced reflection multiplier. The capacitance  $C$  shown in the circuit is the sum of the diode junction capacitances and parasitic contributions from the diode package.

exceed the saturated velocity. Resistive frequency multipliers, however, can operate at frequencies in the infrared region [16].

In this paper, we propose and calculate the performance of a new resistive balanced reflection multiplier capable of efficient wide-band odd-harmonic multiplication at submillimeter wavelengths. We develop a closed-form distributed analysis for determining the harmonic conversion efficiency and the sensitivity of the conversion efficiency to parasitic capacitance and inductance. Also, our analysis is used to compare the conversion efficiency of our reflection-type resistive balanced multiplier with an ideal resistive balanced transmission multiplier. Our results for the transmission-type resistive multiplier are consistent with those of Benson and Frerking [5]. These authors used a large-signal analysis program to determine the theoretical efficiency of a tripler using a nonideal varistor diode and a generalized embedding network. Our model is considerably simpler and offers physical understanding because it computes the steady-state harmonic voltages in closed form. Design guidelines are obtained from our analysis.

## II. MODELING THE RESISTIVE BALANCED REFLECTION MULTIPLIER

Fig. 1 illustrates a schematic diagram of the resistive balanced reflection multiplier circuit. It consists of a transmission line terminated with an antiparallel diode pair. Parasitic inductance and capacitance in the transmission line termination are included.

Neglecting the effects of parasitic inductance and capacitance, the reflected waveform can be determined in closed form by equating the current through the transmission line to the current through the load in the following way:

$$\frac{v_+ - v_-}{Z_0} = I_{01} \left\{ \exp \left( \frac{V_D}{V_T} \right) - 1 \right\} - I_{02} \left\{ \exp \left( - \frac{V_D}{V_T} \right) - 1 \right\} \quad (1)$$

where  $v_+$  and  $v_-$  are the voltage normal modes of the transmission line,  $V_D = v_+ + v_-$ , and  $V_T$  is the thermal voltage  $kT/q$ . Normalizing the incident, reflected, and diode voltage waveforms to the thermal voltage ( $u_{\pm} = v_{\pm}/V_T$ ) and grouping constants into a characteristic constant,  $U_0 = Z_0 I_0/V_T$ , results in

$$u_+ - u_- = U_0 [\exp(u_D) - \exp(-u_D)] \quad (2)$$

where the reverse saturation currents of the balanced antiparallel diodes are assumed equal. Further simplifying (2) by grouping the exponential terms in the form of the hyperbolic sine results in a function  $f$ ,

$$f(u_+, u_-) = 2U_0 \sinh(u_+ + u_-) + u_- - u_+ = 0 \quad (3)$$

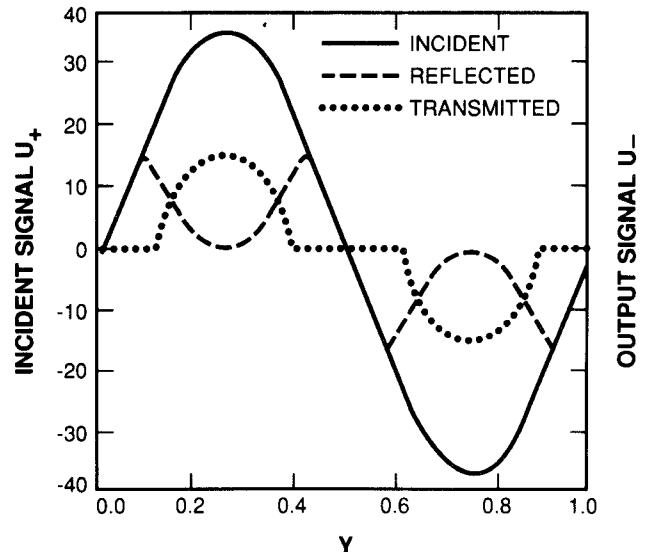

whose roots determine the reflected voltage waveform given some incident wave  $u_+$ . Fig. 2 shows the incident and resulting reflected waveforms when a sinusoidal wave,  $u_+ = A \sin(2\pi y)$ , of amplitude  $A = 37$  ( $V_T = 25$  mV,  $v_+ = 0.925$  mV) is assumed to be incident on the antiparallel diodes. Note that the reflected wave changes sign when the diode load impedance crosses over

Fig. 2. Superposition of the incident and output normalized voltage waveforms of the reflection and transmission multipliers. The reflection multiplier's output voltage waveform has a frequency three times that of the incident voltage waveform, indicating a large third-harmonic component.

the line impedance  $Z_0$ , and one can intuitively see that it has a large third-harmonic component. The symmetry of the antiparallel diodes permits the generation of only odd harmonics. Each diode works as an idler, effectively short-circuiting the other at even harmonics.

The normalized odd Fourier components calculated from the reflected wave are

$$u_-(n\omega) = 2 \int_0^1 u_-(y) \sin(n2\pi y) dy \quad (4)$$

where the variable  $y$  is the frequency-time product,  $f * t$ , and where the integration is performed over one period of the fundamental. The percent harmonic conversion efficiency as a function of the incident voltage amplitude and the diode parameters is given by

$$\eta(n\omega) = \left| \frac{u_-(n\omega)}{A} \right|^2 \times 100. \quad (5)$$

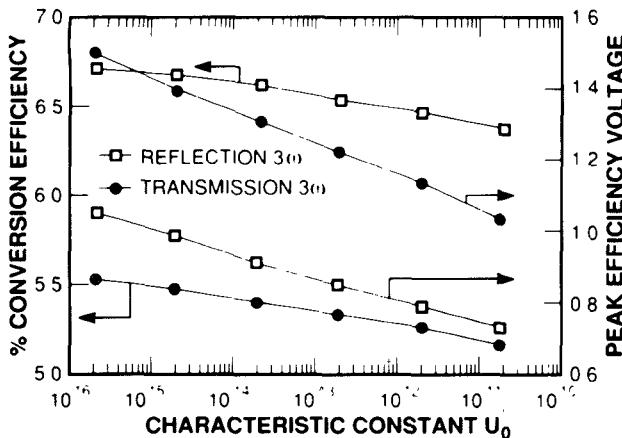

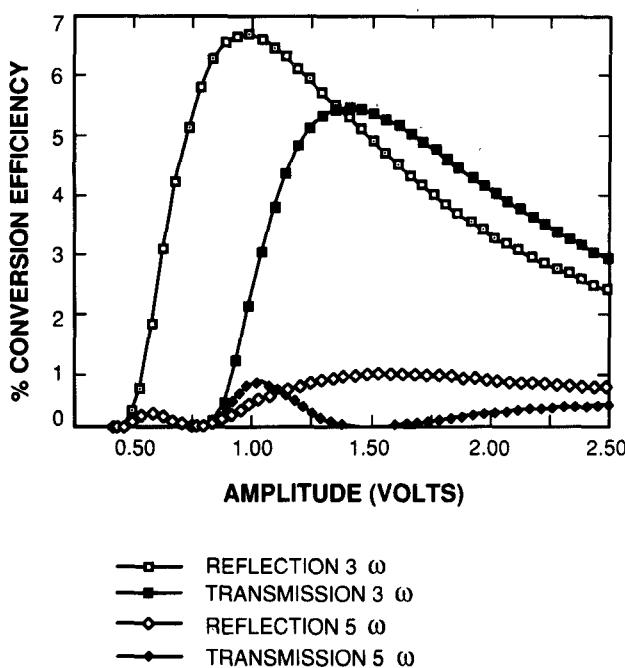

The Newton-Raphson method [17] was used to determine the reflected waveform in (3). The odd Fourier components of the reflected voltage waveform were determined by solving (4) numerically. Fig. 3 illustrates the peak third-harmonic conversion efficiency and the corresponding peak efficiency voltage as a function of the characteristic constant for the reflection multiplier. As the characteristic constant increases, the peak conversion efficiency and the peak efficiency voltage both decrease slightly. The conversion efficiency, therefore, decreases as the characteristic impedance increases, and it also decreases as the temperature increases because the product  $I_0/T$  varies exponentially with the temperature. Fig. 4 illustrates the third- and fifth-harmonic conversion efficiency versus amplitude curves of the reflection multiplier with a characteristic constant equal to  $U_0 = 10^{-15}$ . The third-harmonic conversion efficiency has a single maximum at 6.7% when the normalized incident amplitude  $A = 37$ , which corresponds to  $v_+ = 0.925$  V. This theoretical peak efficiency is close to that reported for measured optimized varactor triplers [18]–[20].

The effects of series parasitic resistance have been examined by a slight extension of the method described in this section.

Fig. 3. The peak third-harmonic power conversion efficiency and the corresponding peak efficiency voltage as a function of the characteristic constant for the reflection and transmission multipliers.

Fig. 4. The third- and-fifth-harmonic power efficiency-amplitude characteristic curves for the reflection and transmission multipliers with a characteristic constant  $U_0 = 10^{-15}$ .

These calculations show that if the parasitic series resistance is kept below 2% of the characteristic impedance  $Z_0$ , then the degradation in the harmonic conversion efficiency from the ideal case will be less than a few percent. For the numerical example discussed above, this restriction implies that the series parasitic resistance must be of the order of  $1 \Omega$ . Such low series resistances can be achieved with recently developed thin-film technology [21]–[23], which makes it possible to fabricate Schotky diodes with substrate thicknesses of less than  $1000 \text{ \AA}$ .

### III. THE EFFECT OF PARASITIC CAPACITANCE AND INDUCTANCE

The effect of finite junction capacitance on the performance of the reflection multiplier was also analyzed. The capacitance  $C$  in Fig. 1 is the sum of the linearized junction capacitance of the diodes. The expression relating the incident and reflected

voltage waveforms is

$$\frac{v_+ - v_-}{Z_0} = C \frac{dV_D}{dt} + I_0 \left[ \exp \left( \frac{V_D}{V_T} \right) - 1 \right] - I_0 \left[ \exp \left( - \frac{V_D}{V_T} \right) - 1 \right]. \quad (6)$$

Normalizing the voltages and grouping the exponential terms in the form of the hyperbolic sine results in

$$\frac{u_+ - u_-}{Z_0} = C \frac{d(u_+ + u_-)}{dt} + \frac{2I_0}{V_T} \sinh(u_+ + u_-). \quad (7)$$

In order to make the results easier to interpret and more general, we normalize the time variable and group the constants into normalized characteristic constants. The resulting equation is

$$\frac{du_-}{dy} = U_1(u_+ - u_-) - 2\pi A \cos(2\pi y) - 2U_0U_1 \sinh(u_+ + u_-) \quad (8)$$

where the variable  $y$  is again defined as the frequency-time product and the normalized capacitance constant  $U_1 = 1/Z_0Cf$ .

The integration of (8) will normally contain both transient solutions and a steady-state solution. For evaluating harmonic generation in the reflected wave we wish to examine only the steady-state solution. This steady-state solution is characterized by the relation

$$u_-(y) = u_-(y + 2\pi).$$

A very close approximation to the initial steady-state starting value  $u_-(0)$  can be obtained from the solution of (8) for the case where the diodes are turned off (i.e.,  $U_0 = 0$ ):

$$u_-(y) = \frac{(U_1^2 - 4\pi^2)A \sin(2\pi y) - (4\pi U_1)A \cos(2\pi y)}{U_1^2 + 4\pi^2}. \quad (9)$$

From this solution we find that the steady-state reflected voltage waveform has an initial phase delay at  $t = 0$  of

$$u_-(0) = -\frac{A}{\pi} \left[ \frac{U_1}{1 + (U_1/2\pi)^2} \right]. \quad (10)$$

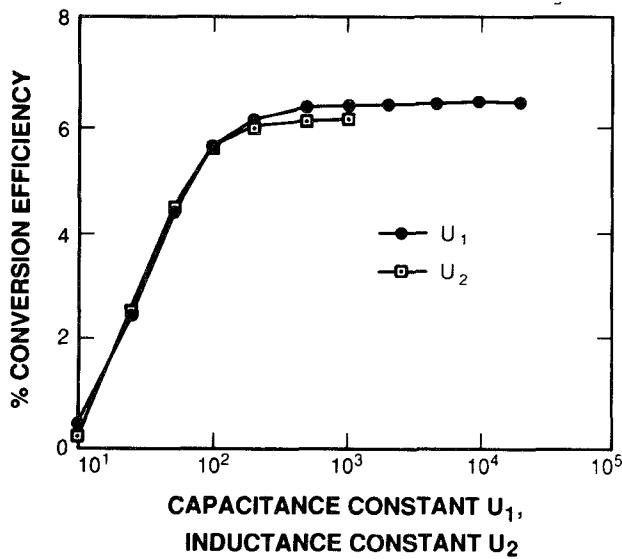

Equation (8) was solved numerically by the Runge-Kutta method for reflected waveforms corresponding to capacitance constants in the range from  $U_1 = 2$  to  $U_1 = 2000$ . In each case it was observed that the reflected waveform starts and finishes at the same value, verifying that the calculated initial conditions corresponded to steady state. Fig. 5 illustrates the third-harmonic conversion efficiency as a function of the normalized capacitance constant  $U_1$ . The efficiency is inversely proportional to the capacitance-frequency product. Maximum efficiency occurs when  $U_1 > 500$ . The efficiency versus amplitude characteristic curves do not change their functional form when finite junction capacitance is included in the model.

The effect of parasitic inductance in the line-to-diode connection on the performance of the reflection harmonic generator was also modeled. This inductance in the reflection multiplier can be modeled by a lumped element connected in series with the load as shown in Fig. 1. The expression relating the incident and reflected voltage waveforms is

$$\frac{v_+ - v_-}{Z_0} = 2I_0 \sinh \left[ \frac{V_D(t)}{V_T} \right] \quad (11)$$

where  $V_D(t)$  is the line voltage  $V_L$  minus the voltage drop across

Fig. 5. The third-harmonic power conversion efficiency for the reflection multiplier as a function of the normalized capacitance-frequency product  $U_1 = 1/Z_0 C f$  and the normalized inductance-frequency product  $U_2 = Z_0 / L f$ .

the parasitic inductance:

$$V_D(t) = (v_+ + v_-) - \frac{L}{Z_0} \left( \frac{dv_+}{dt} - \frac{dv_-}{dt} \right). \quad (12)$$

Normalizing the voltages and time derivatives and grouping parameters into the characteristic constants  $U_0 = Z_0 I_0 / V_T$  and  $U_2 = Z_0 / L f$ , we obtain the differential equation

$$\frac{du_-}{dy} = U_2 \left[ \sinh^{-1} \left( \frac{u_+ - u_-}{2U_0} \right) - (u_+ + u_-) \right] + 2\pi A \cos(2\pi y) \quad (13)$$

for which numerical solutions were obtained in a manner similar to the previous cases.

Fig. 5 illustrates the third-harmonic conversion efficiency as a function of the normalized inductance constant  $U_2$ . The harmonic efficiency is inversely proportional to the inductance-frequency product. The maximum conversion efficiency occurs when  $U_2 > 500$ . The efficiency-amplitude characteristic curves do not change their functional form when a finite load inductance is included in the model.

The combined effect of junction capacity and load inductance was also studied. In this case, the expression relating the incident and reflected voltage waveforms is a second-order differential equation. The derivation is a straightforward extension of the previous two examples. The expression relating the incident and reflected voltage waveforms of the reflection multiplier with parallel junction capacity and series load inductance is as follows:

$$\begin{aligned} \frac{d^2 u_-}{dy^2} &= \frac{d^2 u_+}{dy^2} - U_2 \left( \frac{du_+}{dy} + \frac{du_-}{dy} \right) + \frac{4\pi^2}{\omega^2 LC} (u_+ - u_-) \\ &\quad - \frac{8\pi^2 U_0}{\omega^2 LC} \sinh \left( u_+ + u_- - \frac{1}{U_2} \left( \frac{du_+}{dy} - \frac{du_-}{dy} \right) \right). \quad (14) \end{aligned}$$

As expected, for zero capacitance (14) reduces to (13), and for zero inductance (14) reduces to (8). This formulation was used

to estimate the limits to the parasitic capacitance and inductance necessary for obtaining near ideal multiplier operation. Maximum efficiency was found to occur when both  $U_1 > 500$  and  $U_2 > 500$ , but only a modest loss in efficiency is incurred if the limit of these constants is reduced to 100. This guideline is useful in designing the resistive balanced reflection multiplier.

#### IV. COMPARISON WITH A RESISTIVE BALANCED TRANSMISSION MULTIPLIER

A resistive balanced transmission multiplier has been described previously [21]. It consists of an input low-pass filter, two antiparallel diodes, and a high-pass output filter. The circuit is designed to pass the fundamental signal through the low-pass filter to the nonlinear element. The multiplied signal is transmitted through the output waveguide and rejected by the low-pass filter. A cutoff waveguide or a coupled line output filter is used to reject the fundamental signal at the output.

When the above analysis of the reflection multiplier is applied to the ideal resistive balanced transmission multiplier, the resulting equation for determining the output waveform is as follows:

$$f(t) = 2\mu_0 \sinh [\mu(t) - \mu_L(t)] - \mu_L(t) = 0 \quad (15)$$

where  $\mu_L(t) = I(t)R/V_T$  and  $\mu_0 = I_0 R/V_T$ .

Parameters were chosen to meaningfully compare this transmission multiplier with our reflection multiplier. A  $50\ \Omega$  load was chosen to match the output circuit to a  $50\ \Omega$  transmission line. This allows the characteristic constants of the reflection and transmission multiplier to be equal. We assume that at the fundamental frequency the low-pass filter presents a source impedance of  $50\ \Omega$  and the high-pass filter presents a short circuit to the diodes. At the third-harmonic frequency we assume the low-pass filter to present a short circuit and the high-pass filter to present a  $50\ \Omega$  load to the diodes. Equation (15) was solved by the Newton-Raphson method. Fig. 2 illustrates both the incident and transmitted normalized voltage waveforms for amplitude  $A = 37$ . Note that the output waveform has the same period as the incident waveform. Fig. 3 illustrates the third-harmonic conversion efficiency and the corresponding peak-efficiency voltage as a function of the characteristic constant. The conversion efficiency decreases with increasing characteristic impedance of the input transmission line and it also decreases as the temperature increases because the product  $I_0/T$  varies exponentially with the temperature. Fig. 4 illustrates the third- and fifth-harmonic conversion efficiency versus amplitude curve of the ideal transmission multiplier. The maximum third-harmonic conversion efficiency for a  $50\ \Omega$  load is equal to approximately 5.4%, which is 23% lower than the reflection design.

#### V. CONCLUSIONS

A resistive balanced reflection multiplier has been proposed which generates an output waveform with a frequency three times that of the incident waveform with an efficiency of 6.7%. This new type of multiplier exceeds the maximum efficiency of the transmission-type multiplier by some 23%. The varactor multiplier, although it has a higher efficiency at lower frequencies, has an inherent frequency limitation arising from the fact that the neutral space-charge boundary has a saturated velocity so the reflection multiplier should be superior at higher frequency ranges. The calculations presented in this paper show that with the thin-film and monolithic fabrication techniques now available the reflection multiplier should be able to realize its superiority at driving frequencies in excess of 100 GHz.

## ACKNOWLEDGMENT

The authors would like to thank Dr. K. A. Rauschenbach for helpful technical suggestions.

## REFERENCES

- [1] S. A. Maas, *Nonlinear Microwave Circuits*. Norwood, MA: Artech House, 1988, pp. 283–319.

- [2] C. Nguyen, “A 35% bandwidth Q-to-W-band frequency doubler,” *Microwave J.*, pp. 232–235, Sept. 1987.

- [3] J. W. Archer and M. T. Faber, “High-output, single- and dual-diode, millimeter-wave frequency doublers,” *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 533–538, June 1985.

- [4] P. Penfield, Jr. and R. P. Rafuse, *Varactor Applications*. Cambridge, MA: M.I.T. Press, 1962.

- [5] K. Benson and M. A. Frerking, “Theoretical efficiency for triplers using nonideal varistor diodes at submillimeter wavelengths,” *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 1367–1374, Dec. 1985.

- [6] M. T. Faber, J. W. Archer, and R. J. Mattauch, “A frequency doubler with 35% efficiency at W band,” *Microwave J.*, vol. 28, pp. 145–152, July 1985.

- [7] M. V. Schneider and T. G. Phillips, “Millimeter-wave frequency multiplier,” *Int. J. Infrared and Millimeter Waves*, vol. 2, pp. 15–22, 1981.

- [8] M. V. Schneider and W. W. Snell, “A scaled hybrid frequency multiplier from 10 to 30 GHz,” *Bell Syst. Tech. J.*, vol. 50, pp. 1933–1942, 1971.

- [9] M. V. Schneider and W. W. Snell, “Hybrid integrated frequency multiplier from 10 to 30 GHz,” *Proc. IEEE*, vol. 58, pp. 1402–1404, 1970.

- [10] C. H. Page, “Harmonic generation with ideal rectifiers,” *Proc. IRE*, vol. 46, pp. 1738–1740, Oct. 1956.

- [11] C. H. Page, “Frequency conversion with positive nonlinear resistors,” *J. Res. Nat. Bur. Stand.*, vol. 56, pp. 179–190, Apr. 1956.

- [12] W. M. Van Loock, “Optimum frequency multiplication with resistive diodes,” *Electron. Lett.*, vol. 10, pp. 158–159, May 2, 1974.

- [13] P. Proksch, “Energetische Beziehungen für Bandbegrenzte Signale in Nichtlinearen Wirkwiderständen,” *Arch. Elek. Übertragung*, vol. 35, pp. 222–224, May 1981.

- [14] D. Leenov and A. Uhlir, “Generation of harmonics and subharmonics at microwave frequencies with P-N junction diodes,” *Proc. IRE*, vol. 46, pp. 1724–1729, Oct. 1959.

- [15] J. M. Manely and H. E. Rowe, “Some general properties of nonlinear elements,” *Proc. IRE*, vol. 44, pp. 904–913, July 1956.

- [16] A. Sanchez, C. F. Davis, K. C. Liu, and A. Javan, “The MOM tunneling diode: Theoretical estimate of its performance at microwave and infrared frequencies,” *J. Appl. Phys.*, vol. 49, no. 10, pp. 5270–5277, Oct. 1978.

- [17] W. H. Press, B. P. Flannery, S. A. Teukolsky, and W. T. Vetterling, *Numerical Recipes: The Art of Scientific Computing*. New York: Cambridge University Press, 1986, pp. 254–259.

- [18] J. W. Archer, “Millimeter wavelength frequency multipliers,” *IEEE Trans. Microwave Theory Tech.*, vol. MTT-29, pp. 552–557, June 1981.

- [19] N. R. Erickson, “A high efficiency frequency tripler for 230 GHz,” in *Proc. 12th European Microwave Conf.*, Sept. 1982, pp. 288–298.

- [20] J. W. Archer, “An efficient 200–290-GHz frequency tripler incorporation in a novel stripline structure,” *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 416–420, Apr. 1984.

- [21] K. Rauschenbach, “The self-aligned opposed gate-source transistor and the distributed thin film harmonic generator,” Ph.D. thesis, Cornell University, 1988.

- [22] K. C. Lee, J. Silcox, and C. A. Lee, “Schottky barrier diode on a submicron-thick silicon membrane using a dual surface fabrication technique,” *J. Appl. Phys.*, vol. 60, no. 11, 1 Dec. 1986.

- [23] K. Rauschenbach and C. A. Lee, “High-resolution resonant refractive index lithography,” *J. Appl. Phys.*, vol. 66, no. 9, pp. 4481–4488, Nov. 1989.

## Scattering Effects in the Dielectric Slab Waveguide Caused by Electrically Dissipative or Active Regions

Thomas G. Livernois, Dennis P. Nyquist,

and Michael J. Cloud

**Abstract**—A polarization electric field integral equation (EFIE) is used to model conducting discontinuities in the dielectric slab waveguide. A complex refractive index accounts rigorously for effects of conduction current in the discontinuity region. Both dissipative and active cases are treated; power balance, based on Poynting's theorem, is used to determine the fractional radiated power in each case. The method of moments is invoked to solve the integral equation. The accuracy of the analysis method is confirmed through comparison of results for the air gap case with those of other recently published methods. Numerical results illustrate application to a typical GaAs ternary system.

## I. INTRODUCTION

Open dielectric waveguide components have become increasingly important research topics. These structures are involved in many crucial aspects of high-frequency integrated circuits. Waveguide discontinuities resulting from these components often give rise to problems in performance [1]; therefore, precise knowledge of discontinuity field behavior plays an important role in component and system design. Several approaches have been used for the analysis of open-boundary waveguide problems, including perturbation methods [2], spectral iterative techniques [3], and finite- and boundary-element methods [4]. A brief literature review may also be found in [4].

This paper treats phenomena associated with scattering from electrically dissipative or active slice discontinuities in the dielectric slab. The apparent absence of published work in this area seems to indicate that the effects of conduction currents within dielectric waveguide discontinuities have not been rigorously studied.

The present work exploits the polarization electric field integral equation (EFIE) formulation described and developed in [5]. The polarization EFIE is solved by the method of moments (MoM), leading to relevant discrete-mode scattering coefficients, and fractional powers (with respect to incident power) scattered, radiated, and dissipated/supplied (in the passive/active case). This method has several advantages over other existing approaches, viz., (1) it is conceptually exact, and (2) it is believed to be computationally less cumbersome than finite-element and related methods.

## II. THEORY

Fig. 1 shows the configuration of the discontinuity region along an open-boundary dielectric slab waveguide. The refractive index profile of a uniform, unperturbed surface waveguide is described by  $n_g$ , while index  $n_s$  characterizes the uniform

Manuscript received January 2, 1990; revised October 23, 1990. This work was supported in part by the National Science Foundation under Grant ECS-86-11958.

T. G. Livernois is with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109.

D. P. Nyquist is with the Department of Electrical Engineering, Michigan State University, E. Lansing, MI 48824.

M. J. Cloud is with the School of Engineering, Lawrence Technological University, Southfield, MI 48075.

IEEE Log Number 9042340.